- 产品详情

CPLD MAX® 系列 600 门 32 宏电池 0.8um 技术 5V 28 引脚窗口 CDIP

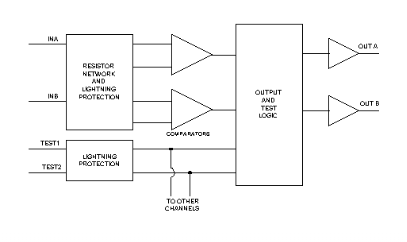

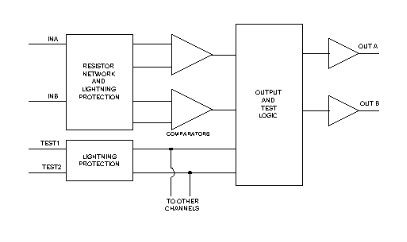

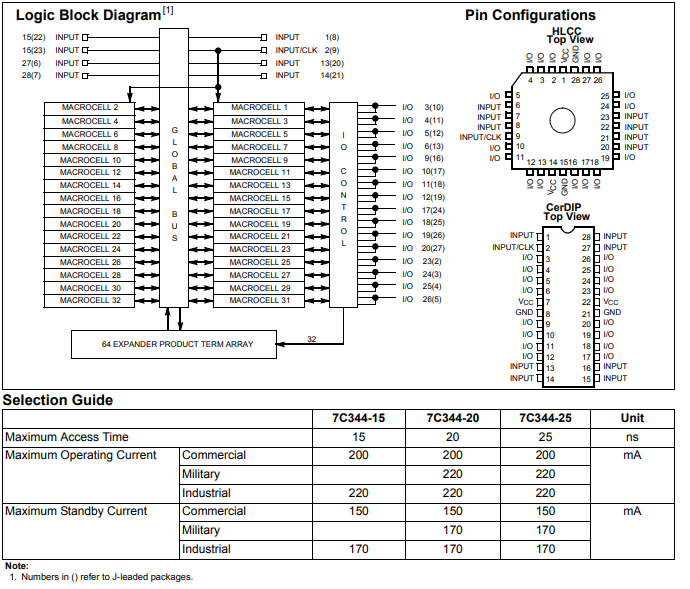

CY7C344具有28引脚,300 mil DIP或加窗j引脚陶瓷芯片载体(HLCC),代表了该尺寸中密度最大的EPLD。8个专用输入和16个双向I/O引脚通信到一个逻辑阵列块。在CY7C344 LAB中有32个宏细胞和64个膨胀产物项。当使用I/O宏单元格作为输入时,使用两个扩展器来创建输入路径。即使所有的I/O引脚都由宏单元寄存器驱动,仍然有16个“埋藏”寄存器可用。所有输入、宏单元和I/O引脚在LAB内相互连接。

CY7C344的速度和密度使其成为所有类型应用的自然选择。仅使用这一个器件,设计人员就可以实现复杂的状态机、注册逻辑和组合“粘合”逻辑,而无需使用多个芯片。这种架构灵活性允许CY7C344取代多芯片TTL解决方案,无论它们是同步的、异步的、组合的还是三者兼而有之。

特性

•高性能,高密度替代TTL,

74HC,以及自定义逻辑

•32个宏细胞,64个扩增产物项在一个LAB中

•8个专用输入,16个I/O引脚

•0.8微米双金属CMOS EPROM技术

•28引脚,300 mil DIP, cerDIP或28引脚HLCC, PLCC封装

Product Technical Specifications

| EU RoHS | Not Compliant |

| ECCN (US) | 3A001.a.2.c |

| Part Status | Obsolete |

| HTS | 8542.39.00.01 |

| Automotive | No |

| PPAP | No |

| Family Name | MAX® |

| Program Memory Type | EPROM |

| Number of Logic Blocks/Elements | 1 |

| Number of Macro Cells | 32 |

| Process Technology | 0.8um |

| Device System Gates | 600 |

| Data Gate | No |

| Maximum Number of User I/Os | 16 |

| Number of Flip Flops | 32 |

| In-System Programmability | No |

| Number of Inter Dielectric Layers | 2 |

| Programmability | Yes |

| Reprogrammability Support | No |

| Maximum Internal Frequency (MHz) | 62.5 |

| Maximum Clock to Output Delay (ns) | 15 |

| Maximum Propagation Delay Time (ns) | 25 |

| Speed Grade | 25 |

| Individual Output Enable Control | No |

| Minimum Operating Supply Voltage (V) | 4.5 |

| Maximum Operating Supply Voltage (V) | 5.5 |

| Typical Operating Supply Voltage (V) | 5 |

| Maximum Operating Current (mA) | 220 |

| Minimum Operating Temperature (°C) | -55 |

| Maximum Operating Temperature (°C) | 125 |

| Supplier Temperature Grade | Military |

| Tradename | MAX |

| Mounting | Through Hole |

| Package Height | 3.56(Max) |

| Package Width | 7.87(Max) |

| Package Length | 37.72(Max) |

| PCB changed | 28 |

| Standard Package Name | DIP |

| Supplier Package | Windowed CDIP |

| Pin Count | 28 |

| Lead Shape | Through Hole |